# DESIGN MOFET BASED TRANSMITTER FOR ONCHIP INTERCONNECTS

# S.Viji<sup>1</sup>, K.Kalarani<sup>2</sup>

<sup>1</sup> PG Scholar, <sup>2</sup>Assistant Professor, Department of VLSI Design, Theni Kammavar Sangam College of Technology, Tamilnadu, (India)

#### **ABSTRACT**

The growing demand for wide bandwidth communication in a serial link transceiver within the integrated circuits calls for large number of high speed inputs and outputs per chip. In serial link transceiver propose various techniques to achieve low swing signals. These techniques are used to transmit the signals through interconnects using different types of drivers and receivers. Objective of this work is design a driver circuit in transmitter using MOSFET. The proposed transmitter achieves less delay compare to repeater insertion method. In driver circuit both current mode and voltage mode multiplexers are used to drive on-chip global interconnects. In voltage mode multiplexer consumes less power than current mode. But current mode has less delay, low swing and achieves wide bandwidth. In this work illustrates current mode driver and to implement some low swing techniques to compare the results such as power, delay, energy, swing, bandwidth. The low swing techniques are Conventional Level Converter (CLC) and Symmetric Source Follower Driver with Level Converter (SSDLC). The proposed transmitter implemented using 180nm technology through simulation with Synopsys HSPICE.

Keywords: Low Swing, Voltage Mode Driver, Current Mode Driver

#### I. INTRODUCTION

In transmitter circuit both voltage and current mode techniques are used to transmit the signals. In order to achieve low swing and propagation delay we propose pseudo NMOS multiplexing based current mode driver and also to implement some low swing techniques. The low swing techniques are conventional level converter and symmetric source follower with level converter. In that proposed techniques driven by a factor of two compare to that using repeater insertion techniques. Transmitter circuit implemented by Hspice simulator using 180nm technology.

## II. SIGNALLING TECHNIQUES

Depending upon the physical arrangement of the wire channels of data links, electrical signaling schemes for data transmission over wire channels can be classified into single ended, fully differential. In an effort to reduce the intrusion of repeater logic, reduce power dissipation, and potentially drive longer distances, differential low swing signaling may be employed. They can also be categorized into voltage mode and current mode signaling schemes on the basis of the carriers of data links.

IJEEE, Volume 07, Issue 01, Jan-June 2015

#### 2.1 Voltage Mode Signalling

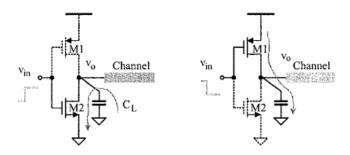

Fig 2.1 Voltage Mode Signaling.

The signal conveyed to the channel by the driver is the output voltage of the inverter. It is determined from

$$C_L \frac{dv_0(t)}{dt} + \frac{dv_0(t) - V_{DD}}{R_v} - C_L V_{OL} \partial(t) = 0 \quad (Risingedge)$$

(2.1)

$$C_L \frac{dv_0(t)}{dt} - C_L V_{OH} \partial(t) + \frac{dv_0(t)}{R_n} = 0 \quad (Fallingedge) \tag{2.2}$$

where Rn and Rp are the channel resistance of the NMOS and PMOS transistors in the triode, respectively, CL is the load capacitance of the driver, VOL and VOH are the voltage of Logic-0 and Logic-1 states, respectively,  $C_LV_{OL}\partial(t)andC_LV_{OH}\partial(t)$  quantify the effect of the initial voltage of the load capacitor at the onset of charging and discharging.

#### 2.2 Current Mode Signaling

Current mode signaling offers the advantages of low supply voltage requirement, a small propagation delay, superior signal integrity, low switching noise, and low power consumption. The single-ended signaling scheme cannot reject the noise coupled to the channels. In addition, the channels of data links with single ended signaling have a large inductance and are sensitive to inductive interferences from other sources.

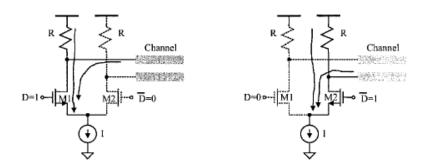

Fig 2.2 Current Mode Signaling.

Fully differential signaling effectively rejects the noise coupled to the channels at the cost of two conductors per channel. Data links with fully differential signaling have a small channel inductance and a low electromagnetic emission. At the receiver side, together with the drawback of voltage-mode signaling, limit data rates. Current

IJEEE, Volume 07, Issue 01, Jan-June 2015

mode incremental signaling, on the other hand, achieves high data rates by utilizing the advantages of the fully differential and current mode signaling schemes. Data links with current mode incremental signaling have a small channel inductance and a low level of electromagnetic emission.

#### III. DRIVER (TRANSMITTER) CIRCUITS

A transmitter circuit encodes a symbol in to current or voltage for transmission over a line. A good transmitter for driving interconnects has output impedance optimized for selected transmission mode.

#### 3.1 Voltage Mode Driver

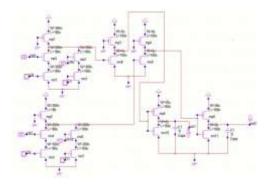

Fig.3.1 Voltage Mode Driver

Transmitter consists of multiplexer, predriver, output driver. The transmitter multiplexes parallel data (D0-D3) generates differential serial data output and drives it to interconnect segment. Pseudo NMOS voltage mode multiplexer requires only one driver for all the inputs. Input data and depending on the selected line the output to be high. The signal is driven by the predriver. Predriver nothing but static inverter used to reduce the output delay and convert full swing signal into limited signal. Finally Output Driver to reduce the swing and reducing power consumption. In Voltage mode driver the capacitor is charging and discharging the signal value is 1F. Similarly the complement signal is generated using the complemented data inputs to output.

# 3.2 Current Mode Driver

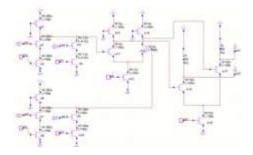

Fig. 3.2 Current Mode Driver

The large size of MOS voltage mode drivers and the large amount of delay and energy consumed by the required predrivers are a significant disadvantage of voltage mode signalling. The current mode drivers are significantly faster and more power efficient than low impedance voltage mode driver. So to reduce output delay, current steering driver should be used with limited swing predriver. It consists of a 4:1 multiplexer, a

IJEEE, Volume 07, Issue 01, Jan-June 2015

preamplifier, and an output driver. The transmitter employs dual pseudo NMOS multiplexers at its input, one for the signal and one for its complement. Each multiplexer input is switched by two series NMOS that are gated by two adjacent clock phases in the same manner that the driver pull downs are gated by adjacent clock phases.

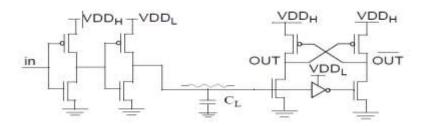

### 3.3 Conventional Level Converter (CLC)

Fig. 3.3 Conventional Level Converter

The driver uses an extra supply with lower voltage to drive the interconnect from 0 to VDDL. The receiver is actually a differential amplifier, with an internal inverter to generate a complementary input signal. This circuit achieves a quadratic energy saving on the interconnect, proportional to VDDL 2.Moreover, VDDL should be large enough to ensure a reasonable noise margin. With VDDH=2.0V, the optimal VDDL for minimum energy delay product is 1.1V, which reduces the overall energy to 40% of that of full swing circuit.

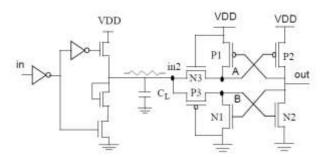

# 3.4 Symmetric Source Follower with Level Converter (Ssdlc)

The circuit of **SSDLC** scheme is shown in Fig.3.4. The driver drives the interconnect with an output swing from Vtn to Vdd- Vtn, shown as node *in2* in Fig.3.4. The threshold voltages are subject to the body effects. The basic idea of the symmetric level converter is similar to the one in Hitachi circuit.

Fig.3.4 Symmetric Source Follower Driver with Level Converter

#### IV. PERFORMANCE CHARACTERISTICS

Table 4.1 Performance Characteristics in avg, peak power, delay

| SCHEME       | AVG        | PEAK POWER | DELAY      |

|--------------|------------|------------|------------|

|              | POWER      |            |            |

| VOLTAGE MODE | 1.0922E-02 | 1.4507E-02 | 2.7351E-10 |

| CML          | 2.3155E-02 | 2.4911E-02 | 1.872E-10  |

| CLC          | 2.8255E-04 | 2.1975E-03 | 5.9459E-10 |

| SSDLC        | 9.9197E-04 | 3.7262E-03 | 1.1097E-10 |

Table 4.1 shows that comparison of average, peak power, and delay. Compare to voltage mode, the current mode logic consume more power but delay reduced. In order to reduce the power CLC and SSDLC techniques to be used.

Table 4.2 Performance characteristics in swing, energy, and rise time fall time

| SCHEME       | SWING      | ENERGY     | RISE & FALL TIME        |

|--------------|------------|------------|-------------------------|

|              |            |            |                         |

| VOLTAGE MODE | 1.8037     | 1.0803E-10 | 2.0102E-10 & 1.8173E-10 |

| CML          | 1.0914     | 2.2922E-10 | 1.6737E-10 & 1.6737E-10 |

| CLC          | 1.9003     | 1.7443E-12 | 8.8059E-11 & 2.9731E-10 |

| SSDLC        | 7.3711E-01 | 5.8785E-12 | -                       |

Table 4.2 shows that comparison of Swing, energy, rise and fall time. Compare to CLC, voltage mode, CML, SSDLC achieve less swing. Less energy achieved by CLC and SSDLC. In SSDLC technique cannot measure rise and fall time because of output goes to low state.

#### V. CONCLUSION

In this work, the differential current mode transmitter for on-chip serial interconnect using pseudo NMOS logic based multiplexer has been proposed. To implement current mode to achieve low swing and delay can be reduced but consumed more power than to voltage mode. So in order to reduce the power, two low swing techniques has been proposed. In summary reducing the swing on interconnect is an effective & powerfull tool for the minimization of energy dissipation but requires a judicious optimization with respect to robustness, design complexity and energy dissipation. As a future, MOSFET has high leakage current due to scaling of transistor at below 32nm technology. So to reduce the leakage current propose CNTFET based transmitter for both voltage mode, current mode driver and to compare the results.

#### **REFERENCES**

- [1] A.P.Jose, G. Patounakis, K.L. Sheppard,"Pulsed current mode signaling for nealy speed of light intrachip communication"IEEE J.Solid state circuits, vol-41, APR 2006.

- [2] Bhaskar, M.; Prasannakumar, D.; Venkataramani, B.," Design of differential voltage mode transmitter for on-chip serial link based on method of logical effort" IEEE conference publication

- [3] C.Kim, D.Burger, and S.W.Keckler, "Non-uniform cache architecture for wire delay dominated onchip caches," IEEE Micro, Vol-23, Dec 2003.

- [4] Ethiopia Nigussie, Juha Plosila, and Jouni isoaho,"Current Mode onchip interconnect using level encoded two phase dual rail encoding"June 2007

- [5] Fei Yuan; Jean Jiang," A pseudo-NMOS fully differential CMOS current-mode multiplexing transmitter for 10 Gb/s serial links circuits and system" Volume:55, July2004

- [6] F.Yuan, "Fully differential 8 to 1 current mode multiplexer for 10Gbit/ss serial links in 180nm cmos" Vol-40, June 2004.

- [7] G.Chen and E.G. Friedman,"low power repeaters driving RC & RLC interconnects with delay and bandwidth constraints"IEEE Tran. Vol.14, Feb 2006.

- [8] Heesoo song, subwan kim& Deog- Kyoon Jeon.,"A reduced swing voltage mode driver for low power multi Gb/s transmitter." Vol-9, June 2009.

- [9] Hui Zhang; Varghese George,; Rabaey, J.M., Low-swing on-chip signaling techniques: effectiveness and robustness. Year-2000, vol-8

- [10] "Hspice signal integrity pdf", 2006/www.synoppsys,com.

- [11] Imed BenDhaou,"Current mode, low power onchip signaling in Deep submicron cmos technology" Vol-50, march2003.

- [12] International Technology Roadmap for Semiconductors, 2009 Edition. Semiconductor industry Association, 2001, interconnects section, p.

- [13] Jongsun kim,"Design of an interconnect architectureand signaling technology for parallelism in communication" Vol-15, Aug 2007.

- [14] John.P.Uyemura,"CMOS Logic Design". Kluwer Publication, 2003.

- [15] L.Zhang, y.Zhang, "high performance on-chip differential signaling for global communication", Jan 2009

# **BIOGRAPHICAL NOTES**

MS.S.VIJI is presently pursuing M.E final year in Electronics and Communication Engineering Department (specialization in VLSI design) from Theni Kammavar Sangam College of Technology, Theni, Tamilnadu, India.

**MS.K.KALARANI** is working as a Assistant Professor in Electronics and Communication Engineering Department, from Theni Kammavar Sangam College of Technology, Theni, Tamilnadu, India.