## Investigation in FIR Filter to Improve Power Efficiency and Delay Reduction

### Mengani Sravanthi<sup>1</sup>, Dr. Kuldeep Bhardwaj<sup>2</sup>

*PG Scholar, Department of Ece Dhruva Institute of Engineering and Technology. Professor & HOD in ECE Dept, Dhruva Institute Of Engineering and Technology.*

### ABSTRACT

In outline of Finite Impulse Response (FIR) channel utilizing snake, coefficients and increase are utilized. Numerous Constant Multiplication (MCM) is the calculation which is utilized as a part of FIR outlining to minimize intricacy of the circuit, expanded deferral and duplication utilizing huge zone. These issues can be upgraded by utilizing new method known as digit-serial different steady duplications. It decreases the multifaceted nature, deferral and region use. Alongside this as of now existed technique, the adjusted convey select snake actualized in the present paper. It demonstrates that there ought to be 10-20% addition in power productivity and half diminishment in postpone contrasted with as of now exist systems.

### I. INTRODUCTION

The increase procedure in the computerized framework is extremely prevalent in designing applications. It is the blend of expansion and moving operation that use more number of machine cycles to execute little augmentation because of reiteration of the terms. To conquer these reiteration issues, the MCM strategy is broadly utilized. Be that as it may, such strategy utilized along the blend of various adders. The structure of MCM along different adders does not deliver culminate answer for power productivity and deferral.

The principal computerized channel (FIR) with various frequencies according to the necessities of client was outlined by James et al. It was outlined utilizing Hilbert Transformation which is under general straight channels classification. This general channels prompts to the issues, for example, inertness, and deferral, time and power utilization.

After this development of usage in computational world, scientists' begun to enhance the FIR channels. Dempster et al actualized the FIR channel in VLSI approach utilizing Bull and Harrick's technique and prevailing into diminishment of time which came about into unpredictability and defer era. To decrease postpone of the FIR, Gallagher et al created the High Radix Booth Multiplier which gave better outcomes as far as the deferral, yet neglected to stay away from the issue of intricacy over bigger channel region thought. It was found that the multifaceted nature in control rationale planning restricting this examination agreeable for the little zone and clock period constraint. To maintain a strategic distance from the above clarify mistakes or requirements the need of distinguishing proof and mix of basic expression created, which was satisfied by Hartley's examination. The method for recognizable proof of the basic expressions known as Canonical Signed Digit (CSD) was presented, that spared the program number by half and by consolidating normal expressions

JEEE

Vol. No. 9, Issue No. 02, July - December 2017

ISSN (O) 2321-2055 ISSN (P) 2321-2045

33% all the more sparing in program tallies was accomplished. The range use and time factors were disregarded in this investigation.

The above review demonstrates that all procedures have the mistakes identifying with time, postponement and power productivity. Till 1996 there was no viable work created in FIR planning. The idea of Hertly was continue promote by Nguyen et al and actualized the move include idea in the Digital Signal Processing/Processors (DSP) with number part idea by alteration. This usage neglects to determine the crosstalk issue. After this the work of FIR in DSP comes into core interest. Also, for this the Multiple Constant Multiplication (MCM) system is utilized which is created by the Potokonjak in February 1996. By using MCM procedure Park et al build up the Computational Sharing Multipliers (CSHM). In which they scale the duplication procedure in vector shape to streamline include and move operation. In any case, he constrains his usage up to circuit level, additionally the circuit level execution require 9.93 mm2 are for every transistor while add up to transistors in circuit are 130K. With this hindrance he not ready to expend less power and less postponement. Voronenko et al likewise show work in computational usage however he additionally not prevailing in execution. This all issue emerges because of long development of expressions, as Hartly just prevail to recognize and consolidate the expression. Aksoy feel free to shape the procedure to dispose of sub expressions in MCM utilizing Boolean Network however in this they not ready to control the postponement with parallel and CSD information.

As per above exchange and study the all papers confronting the issue of vitality utilization and the postponement. From above writing overview, the consideration had given to the utilization of MCM system with Graph Based (GB) technique. It needs to enhance and this paper adds to incorporate those procedures. The blend of this two along arrangement of 0 Integrated Linear Programming (ILP) Problem was utilized. These strategies are utilized along Carry Select Adder (CSA) which gives the better outcomes. The proposed work has been talked about in segment II. Likewise the required segment important to execute FIR channel with CSA clarified in a similar segment. The segment III investigates the all outcomes and exchange. The finish of the exploration with future course was specified in area IV.

### **II. PROPOSED WORK**

### A. Foundation

From the investigation of cases present in reference of FIR usage demonstrates that halfway items in GB calculation prompts to best aftereffects of region lessening at door level.

The moving operation in MCM utilizes D flip-flops, as this procedures deal with bits parallel calculation it is free from equipment. Thus, to share of move, expansion and subtraction operation the abnormal state calculations created in digit-serial MCM outline. From the Study it inferred that science digit-serial administrators possess less region and are free of the information word length, digit-serial structures offer option low many-sided quality plans when contrasted with bit-parallel designs. For the usage of the idea we utilized the GB strategy.

As CSD having 33% lessening in nonzero components when contrasted with twofold. So to expand the adequacy of code, Sign Digit (SD) was utilized. It help in DSP to get low power productive, fast number juggling

Vol. No. 9, Issue No. 02, July - December 2017

ISSN (O) 2321-2055 ISSN (P) 2321-2045

structure and decrease territory utilization [12]. In this the numbers get spoke to into set of  $\{1, 0, -1\}$  and they should be as beneath,

1. A couple of non-zeros digits do not show up.

2. Non-zero components must be equivalent to (n+1)/2, where n is digit number.

The Boolean capacity is essential part of any framework for executing the circuit, and it spoke to by the corresponding recipe which spoke to by Conjunctive Normal Form (CNF) [13]. After this the arithmetical course of action of the bit ought to be done utilizing the Digital Series Arithmetic (DSA). In DSA the bits are partitioned into d-bits and prepared serially by applying every piece in parallel way. It beats the drawback of both individual serial and parallel execution. In this paper, postponement and territory diminishment strategy is concocted along these lines DSA technique is utilized. Along this to accomplish the objective, after as of now predefine [14] strategies are used.

### 1) Exact Common Sub expression Elimination (CSE) algorithm

These algorithms can be formed using the steps mentioned below

a) Detection of partial terms

b) Construction of the Boolean network

c) Formalization of 0-1 IPL problem

d) Then determine the minimum area solution

### 2) GB Algorithm

For the implementation of FIR with CSA, only consider main part of the MINAS-DS algorithm given below,

MINAS-DS(T)  $\mathbf{R} \leftarrow \{1\}$ (R,T) = Synthesize (R,T)While  $T \neq \emptyset$  do For j = 1 TO 2BW + 1 - 1 Step 2 do If  $j \notin R$  and  $j \notin T$  then  $Impcostj = ComputeCost({j},R)$ If Impcostj  $\neq 0$  then  $A \leftarrow R U \{ j \}$ ImpcostT = ComputeTCost (T,R) Iccost j = impcost j + impcost Tend if end if end for find the intermediate constant, ic, with the minimum Iccost j cost among all possible constants, j  $R \leftarrow R \mathbf{U} \{ic\}$ (R,T) = synthesize (R,T)end while D = synthesizeMinArea(R)Return D

Vol. No. 9, Issue No. 02, July - December 2017

ISSN (O) 2321-2055 ISSN (P) 2321-2045

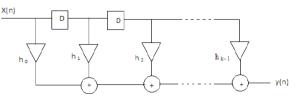

1) FIR filter

**B.** Implementation

Fig.1. FIR filter implementation

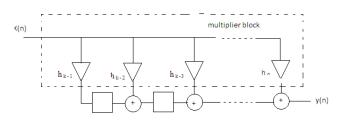

The above architecture has similar complexity in hardware. Hence, we go for the implementation of transposed form FIR filter with generic multipliers. The multiplier block of the digital FIR filter in its transposed Form, where the multiplication of filter coefficients with the filter input is realized, has significant impact on the complexity and performance of the design because a large number of constant multiplications are required. So just collect all multiplication operation together and name it as multiplier block Fig. 2. This is shown below,

### Fig.2. Multiplier block that collects all multiplication operation together

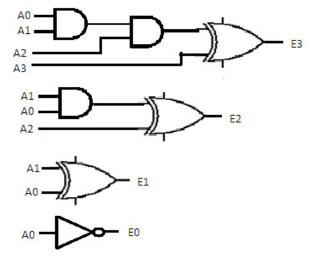

### 2) CSA

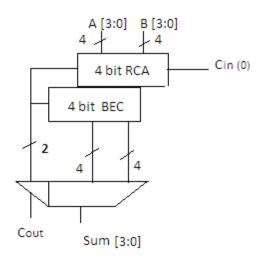

This is used for getting more precise result than already exist methods. In carry select adder we use two Ripple Carry Adder (RCA) to produce the output along with full adder circuit.

It has complex circuit with high propagation delay of ripple carry adder. So instead of using two RCA in CSA, combination of one RCA and one Binary to Excess Converter (BEC) is used. But to replace "n bit "RCA "n+1 bit" BEC require. For 4 bit system following Fig. 3 shows the implementation of BEC.

Fig.3. BEC implementation for 4 bit

USE CONTRACTOR

Vol. No. 9, Issue No. 02, July - December 2017

ISSN (O) 2321-2055 ISSN (P) 2321-2045

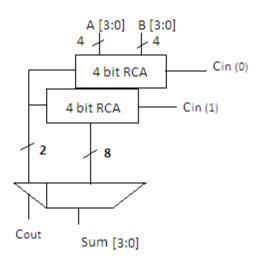

To replace the one RCA circuit with BEC, first need to implement or simplify the CSA using two RCA. This implementation show in below Fig.4.

### Fig.4. Implementation of CSA with two RCA

In the above circuit to eliminate the disadvantages of RCA and make the circuit according to specification which is describe in the whole paper. Replace one RCA with BEC then circuit become Fig. 5.

Fig.5. Replacement of RCA with BEC

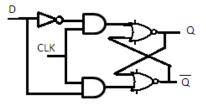

### 3) D-latch

RS flip-flop works as basic fundamental blocks for D flip-flop. It consists of single input (D) driven from S input of RS flip-flop and another is D from R. With this strategy input combination error are reduced. The enable input is second input for D flip-flop which help f/f to hold. This is ANDed with D input. The holding condition occurs when enable is 0 resulting in R=0 and S=0 and if it is 1 S=D and R =D . That is output of system in this condition equals to D. When enable goes to 0, the output remains in previous state.

The working of it indicates that it changes only for or rising falling edge of clock. Also it stores the data which is advantageous for us for implementing the FIR. As it only do the work of passing the output of BEC and RAC combination to the multiplexer but, due to this advantage of the latch, the delay of circuit get reduces. The position of this component exactly below the BEC can be observed from Fig. 6.

Int

Vol. No. 9, Issue No. 02, July - December 2017

ISSN (O) 2321-2055 ISSN (P) 2321-2045

| Input |   | Output         |

|-------|---|----------------|

| D     | Q | $\overline{Q}$ |

| 0     | 0 | 0              |

| 0     | 1 | 1              |

| 1     | 0 | 0              |

| 1     | 1 | 1              |

### Fig.6. Dlatch

### 4) Full adder and subtractor

These two components are used to implement the sifting and adding operation. As probably the FIR filter is form by MCM (Multiple Constant Multiplication) concept. It is the method in which, the number of variables are reduce and the speed of multiplication improves. Also it shows the multiplication of set of variables with the particular constants. In FIR filter it detects the common addition and subtraction operation and reduces them to improve speed of the execution, which helps to reduce the delay in somewhat manner.

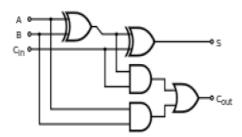

### a) Full Adder

It is used for the addition of binary numbers and produces two output sum and carry. The gate structure is shown in Fig. 7. It consists of A and B inputs, Cin is the carry of least significant bit. S and Cout are the outputs of Sum and Carry respectively.

|   | Input |     | Output |   |

|---|-------|-----|--------|---|

| Α | В     | Cin | Cout   | S |

| 0 | 0     | 0   | 0      | 0 |

| 1 | 0     | 0   | 0      | 1 |

| 0 | 1     | 0   | 0      | 1 |

| 1 | 1     | 0   | 1      | 0 |

| 0 | 0     | 1   | 0      | 1 |

| 1 | 0     | 1   | 1      | 0 |

| 0 | 1     | 1   | 1      | 0 |

| 1 | 1     | 1   | 1      | 1 |

|   |       |     |        |   |

Fig.7. Full Adder

### Vol. No. 9, Issue No. 02, July - December 2017

### ISSN (O) 2321-2055 ISSN (P) 2321-2045

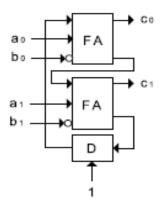

To increase number of bits (2n) the single bit adder must be place in cascade to get desire output. Typical representation of Carry and Sum along with relation between them as given in (3).

**Fig.8. Subtraction Operation**

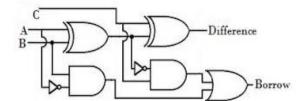

The full subtractor is combinational circuit which is used to perform subtraction of three bits A, B and C shown in Fig. 9. It has three inputs, A (minuend) and B (subtrahend) and C (subtrahend) and two outputs D (difference) and Borrow; D=A-B-C (neglecting the sign convention) Borrow = 1 If A < (B+ZC)

The logic diagram and truth table shown below,

| Input |   | Output |      |      |

|-------|---|--------|------|------|

| Α     | В | С      | Diff | Bor. |

| 0     | 0 | 0      | 0    | 0    |

| 0     | 0 | 1      | 1    | 1    |

| 0     | 1 | 0      | 1    | 1    |

| 0     | 1 | 1      | 0    | 1    |

| 1     | 0 | 0      | 1    | 0    |

| 1     | 0 | 1      | 0    | 0    |

| 1     | 1 | 0      | 0    | 0    |

| 1     | 1 | 1      | 1    | 1    |

### **III. IMPLEMENTATION EXAMPLE**

Detail explanation of solving FIR filter coefficient for simplifies the structure with the help of CSE. The filter coefficient with value h0 = 110011010101, h1 = 001010101011, h2 = 011010101010, h3 = 101010100011 resulted as (6) below,

In

Vol. No. 9, Issue No. 02, July - December 2017

ISSN (O) 2321-2055 ISSN (P) 2321-2045

$\begin{aligned} & 2^{-1}X_3 + 2^{-5}X_1 + 2^{-6}X_7 + \\ & \{2^{-3}X_7 + 2^{-11}X_3\}h[-1] \\ & +\{2^{-2}X_6 + 2^{-7}X_6\}H[-2] \\ & +\{2^{-1}X_7 + 2^{-11}X_3\}H[-3] \end{aligned}$

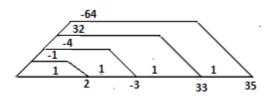

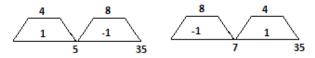

Before providing to CSA equation 6 was plotted (Fig. 10 and Fig. 11). It shows the different combination with minimum number of shift and add structure. For implementation from above equation consider final value of h0 (100011000000)2 and h1 (00100000010)2. Then convert it into decimal for simplicity h0 (812)10 and h1 (202)10. It is time and space consuming to show multiplication using GB. Therefore following example in Fig. 10 and Fig. 11 shows exact method.

This equation further provided to CSA which generate final output. The algorithm run in Xilinx 14.2 shows RTL sketch of final GB algorithm with CSA and design summary.

Fig. 10. General GB Representation

Fig.11. Simplified Structure of GB Representation

### IV. RESULT AND DISCUSSION

In this paper, primary focus is on reduction of the power consumption and delay along reduction in area. In this, the BEC method used to simplify the addition as well as the GB method that produces great output using less computation resources. BEC method is implemented in VHDL coding and executed using the Xilinx software. The above screen shot shows the difference between the two techniques (CSE and GB). It shows the number of the cycle's utilization and the amount of data utilized by the particular variables.

| Current Simulation<br>Time: 1001 nz |     | 200 na 210 na 220 na 230 na 940 na 230 na 260 na 270 na 260 na 280 na 280 na 1000 na |

|-------------------------------------|-----|--------------------------------------------------------------------------------------|

| = 24 x(3; 0)                        |     |                                                                                      |

| AL (1)                              |     |                                                                                      |

| (تې ا <u>چ</u>                      | 1   |                                                                                      |

| 31 x(1)                             |     |                                                                                      |

| (0)                                 |     |                                                                                      |

| 84 y1(7.0)                          | 110 | 133                                                                                  |

| 21 yr [7]                           |     |                                                                                      |

| a 710                               | 1   |                                                                                      |

| <mark>81</mark> #161                | 1   |                                                                                      |

| 31 y1[4]                            |     |                                                                                      |

| <b>6</b> . 7101                     | •   |                                                                                      |

| <b>31</b> v1(8)                     |     |                                                                                      |

|                                     |     |                                                                                      |

| 91 A1[0]                            | 0   |                                                                                      |

| # 24 y2(8.0)                        | 172 |                                                                                      |

|                                     |     |                                                                                      |

### Fig.12. Output of GB using CSA+BEC

It was shown that as number of the variable are more in GB algorithm; still we got minimum number of the data utilization. The further results generated by the implementation of the above two methods for FIR in Xilinx shown in below graphs.

Vol. No. 9, Issue No. 02, July - December 2017

ISSN (O) 2321-2055 ISSN (P) 2321-2045

FIR filter is important part of the DSP system and it widely used implemented to any VLSI and the Communication circuits. In the current research, we have presented the GB method along with the CSA which uses combination of RCA and BEC that gives better results. It improves delay by 48% and 50% CSE and GB components respectively as compared with CSA. Power efficiency was increased by 56% and 64% in CSE and GB respectively as compare to CSE and GB using CSA. This work was limited to the simulation. The experimental implementation on hardboard would add more impact in this research.

### REFERENCES

- [1] J. McClellan, T. Parks, and L. Rabiner, "A computer program for designing optimum FIR linear phase digital filters," *Audio Electroacoust.* ..., 1973.

- [2] A. G. Dempster, S. Member, M. D. Macled, and A. G. Representation, "Blocks in FIR Digital Filters," vol. 42, no. 9, 1995.

- [3] W. L. Gallagher and E. E. Swartzlander, "High Radix Booth Multipliers Using Reduced Area Adder Trees," pp. 545–549, 1995.

- [4] R. I. Hartley, "Subexpression Sharing in Filters Using Canonic Signed Digit Multipliers," vol. 43, no. October, 1996.

- [5] H. T. Nguyen and A. Chatterjee, "Number-Splitting with Shift-and-Add Decomposition for Power and Hardware Optimization in Linear DSP Synthesis," vol. 8, no. 4, pp. 419–424, 2000.

- [6] M. Potkonjak, M. B. Srivastava, and A. P. Chandrakasan, "Multiple Constant Multiplications: Efficient and Versatile Framework and Algorithms for Exploring Common Subexpression Elimination," *IEEE Trans. Comput. Des. Integr. CIRCUITS Syst.*, vol. 15, no. 2, 1996.

- [7] H. Applications, J. Park, W. Jeong, H. Mahmoodi-meimand, S. Member, Y. Wang, H. Choo, and K. Roy, "Computation Sharing Programmable FIR Filter for," vol. 39, no. 2, pp. 348–357, 2004.

- [8] Y. Voronenko and M. Püschel, "Multiplierless multiple constant multiplication," ACM Trans. Algorithms, vol. V, pp. 1–39, 2005.

- [9] L. Aksoy, S. Member, E. Costa, and P. Flores, "Exact and Approximate Algorithms for the Optimization of Area and Delay in Multiple Constant Multiplications," vol. 27, no. 6, pp. 1013–1026, 2008.

- [10] Z. Milivojević, "FIR Filter," in Digital Filter Design, 1st ed., Mikro Elektronika, 2009.

- [11] L. Aksoy, C. Lazzari, E. Costa, P. Flores, and J. Monteiro, "Efficient shift-adds design of digit-serial multiple constant multiplications," *Proc. 21st Ed. Gt. lakes Symp. Gt. lakes Symp. VLSI - GLSVLSI '11*, vol. 2, p. 61, 2011.

### **ABOUT AUTHORS**

**Mengani Sravanthi** is currently pursuing her M.Tech (VLSI) in VLSI Department, DHRUVA Engineering College, Toopranpet, Telangana.

**Dr. Kuldeep Bhardwaj** is currently working as an Associate Professor in VLSI Department, DHRUVA Engineering College, Toopranpet Telangana. His research includes networking and data mining.